跨时钟域包括控制信号(1bit)传输和数据(多bits)传输

单bit信号传输

电平传输:采用两级触发器同步

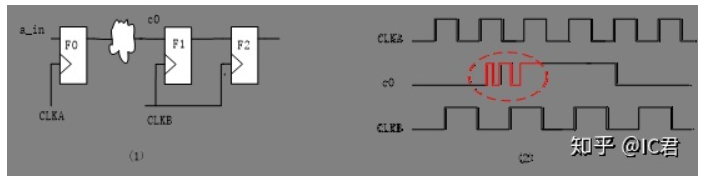

使用误区:知乎CDC

- 时钟域A的组合逻辑信号直接敲两级DFF同步到时钟域B,A的输出必须是时序逻辑,不然容易产生脉冲

- Clock-gating enable 信号没有经过异步处理。

- 时钟域A的组合逻辑信号直接敲两级DFF同步到时钟域B,A的输出必须是时序逻辑,不然容易产生脉冲

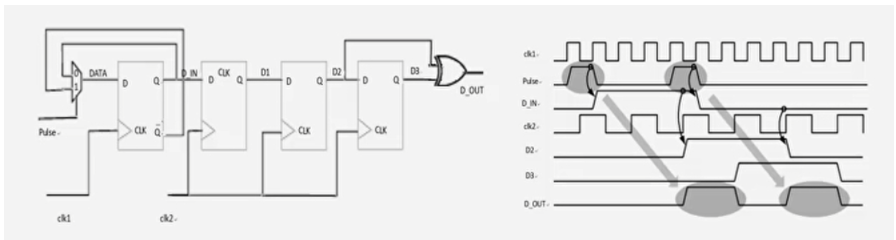

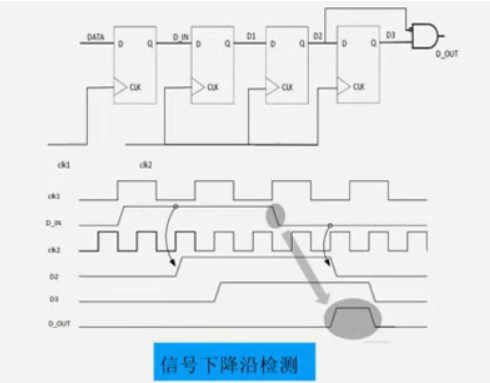

- 脉冲传输:首先将脉冲信号转化为电平信号,采用双触发器同步电平信 号,最后用电平变化检测电路将上升沿下降沿检测输出脉冲信号

快到慢

- 电平展宽

采用脉冲同步器(要求:单脉冲信号,两个有效信号时间间隔大于等于两个同步器时钟周期)

- 快时钟域中需要同步的信号是脉冲信号,它触发原时钟域的反转电路,每当翻转电路收到脉冲时,电路翻转一次慢时钟域的同步器对翻转后的信号进行采样,和边沿检测,重新在本时钟域恢复出脉冲信号

- 快时钟域中需要同步的信号是脉冲信号,它触发原时钟域的反转电路,每当翻转电路收到脉冲时,电路翻转一次慢时钟域的同步器对翻转后的信号进行采样,和边沿检测,重新在本时钟域恢复出脉冲信号

- 握手处理

慢到快

- 两级触发器采样

- 握手处理(平率2倍以下)

- 边沿检测同步器(避免多次采集到有效信号)

多bits数据传输

无法进行打拍同步

- 如果多bits信号间有关系且在一定时间内是确定稳定的,可以取一个信号作为控制使能信号,打两拍同步

采用格雷码

- 通过编码方式将多位信号转化为每次只有一位变化的信号,将“多比特”的跨时钟域变换成“单比特”进行处理。

- 异步FIFO

- 握手信号

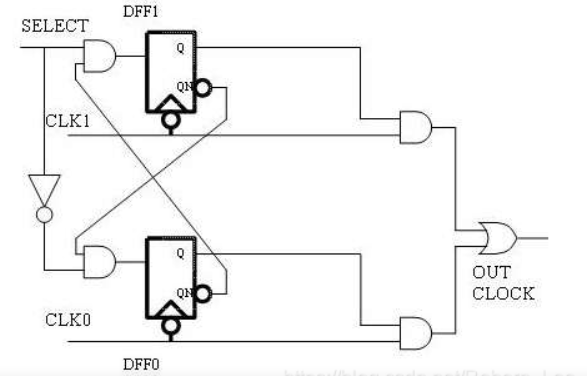

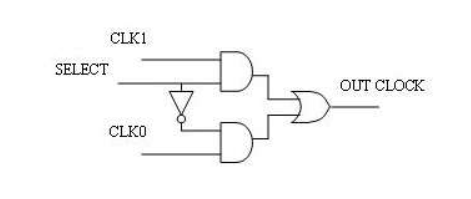

时钟无毛刺切换

- 无毛刺时钟切换电路,又称Glitch free 电路

- 可解释为通过一个选择信号select,二选一选中其中一个时钟信号作为输出信号

- 两个时钟信号间的不同关系可以得到如下分类

毛刺时钟

- 利用纯组合逻辑输出

assign clk_out = (sel&&clk1)||(~sel&&clk0);逻辑电路如下所示

问题:sel信号组合输出产生毛刺现象

时钟相位相关

- 通过寄存器将sel信号与clkx信号对齐,再组合输出

always@(negedge clk0 or negedge rst_n)begin

if(!rst_n)

out0 <= 1'b0;

else

out0 <= ~sel&&~out1;

end

always@(negedge clk1 or negedge rst_n)begin

if(!rst_n)

out1 <= 1'b0;

else

out1 <= sel&&~out0;

end

assign out_clk = clk1&&out1 || clk0&&out0;电路如下